Interface Circuit Type sicut TTL interface, in LVDs interface Circuit etiam divisa in duas modos: Una-alveo RGB data tradenda et impar / etiam pixel-alveo, I-Pixel LVDs et II-Portus LVDs). Si numerus output bits (6bit, 8bit, 10Bat) consideretur, genera LVDs interface circuitus potest dividitur in sequentibus generis:

I. Una VI-bit LVDs frenum interface

est ad eiciam a 6bit LCD Panel et transmit RGB data in una alveo. Etiam notum est XVIII-bit (VI bits quisque pro R, G, et B) LVDs interface.

II. Dual VI-bit LVDs interface

est ad eiciam a 6bit LCD Panel et transmit RGB data in dual via impar / etiam elementa. Etiam notum est XXXVI frenum (VI bits ad impar / etiam RGB) LVDs interface.

III. Una VIII-bit LVDs interface

est ad eiciam 8bit LCD Panel et transmit RGB data in uno modo. Etiam vocavit XXIV-bit LVDs interface.

IV. Dual VIII-bit LVDs interface

est ad eiciam 8bit LCD Panel, et usum impar / etiam pixel dual via ad transmit RGB data. Etiam vocavit XLVIII-bit LVDs interface.

V. Una X-bit LVDs interface unum

X-bit LVDs interface est ad eiciam a X-bit lcd panel et transmit X-bit rgb data (r9 ~ b9, Ite-G9, B0 ~ b9) in unum alveo.

VI. Dual X-bit LVDs interface

dual X-bit LVDs interfaces sunt ad eiciam X-bit lcd tabulata, et uti Dual-frenum traductionem X-bit ~ b09, geo ~ ge9, beo ~ b9, geo ~ ge9, beo ~ beo9, geo ~ ge9, beo ~ b9, geo ~ Ge9, beo ~ b9, geo ~ ge9, beo ~ b9, geo ~ Ge9, beo ~ b9, geo ~ Ge9, beo ~ beo9, geo ~ Ge9, beo ~ beo9, geo ~ ge9, beo ~ b9, geo ~ ge9, beo ~ geo ~ Ge9, beo ~ b. ~ geo ge9, beo ~ beo9, geo ~ Ge9, beo ~ geo ~ Ge9, beo ~ geo ~ ge9, beo ~ beog

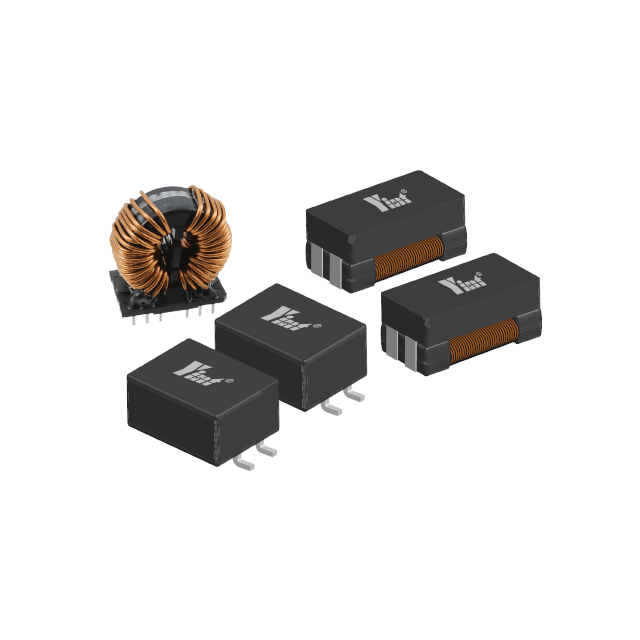

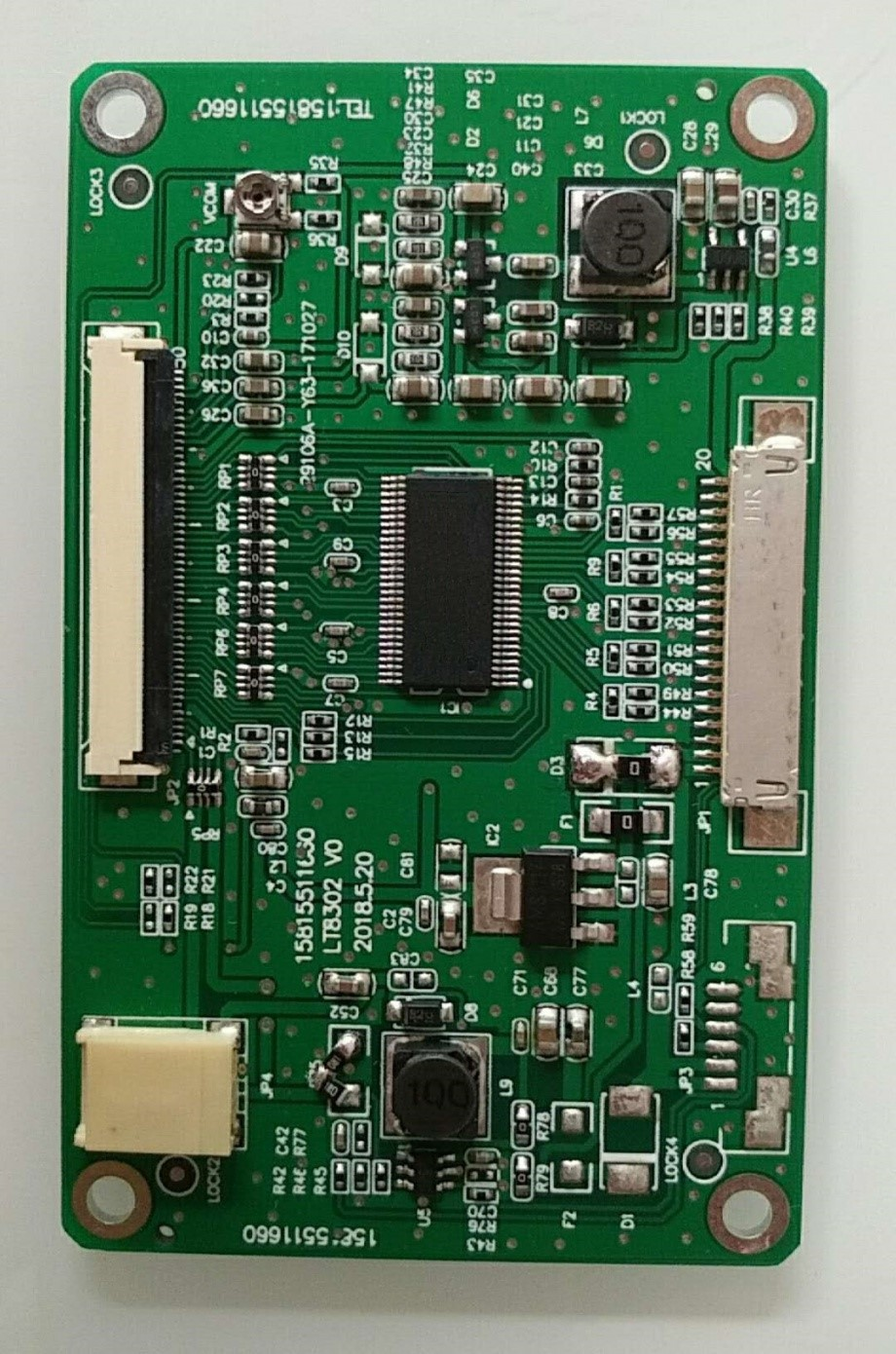

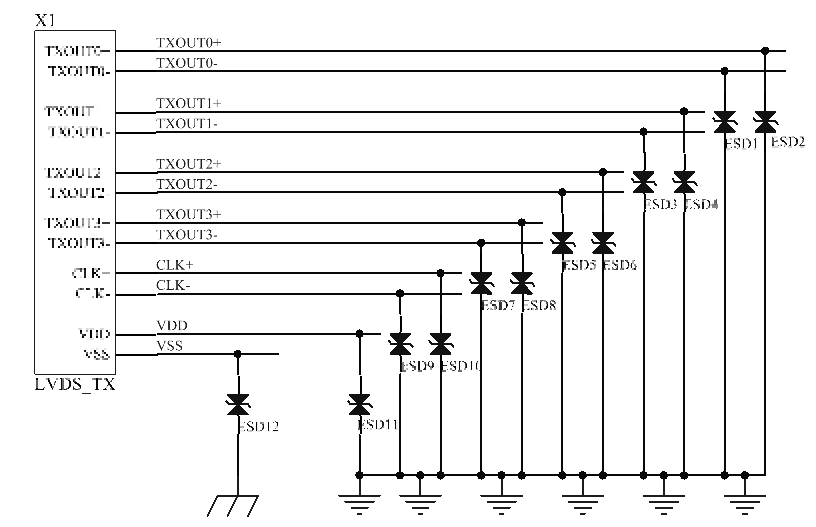

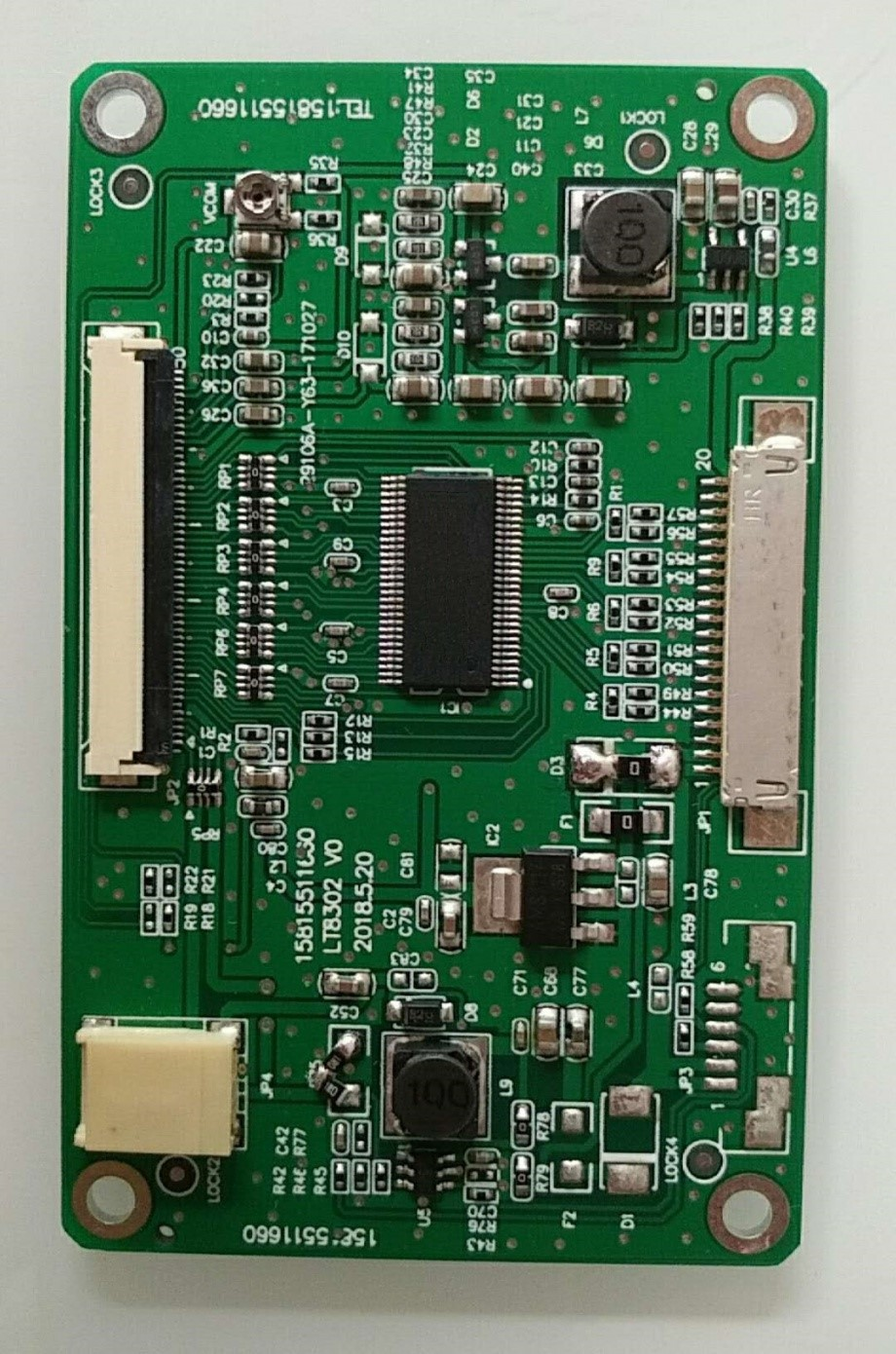

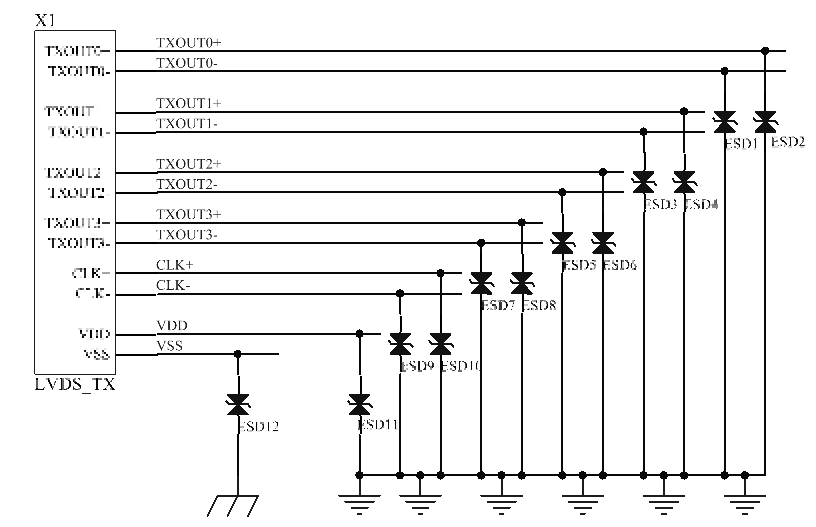

LVDs Donec Circuit Reference Design

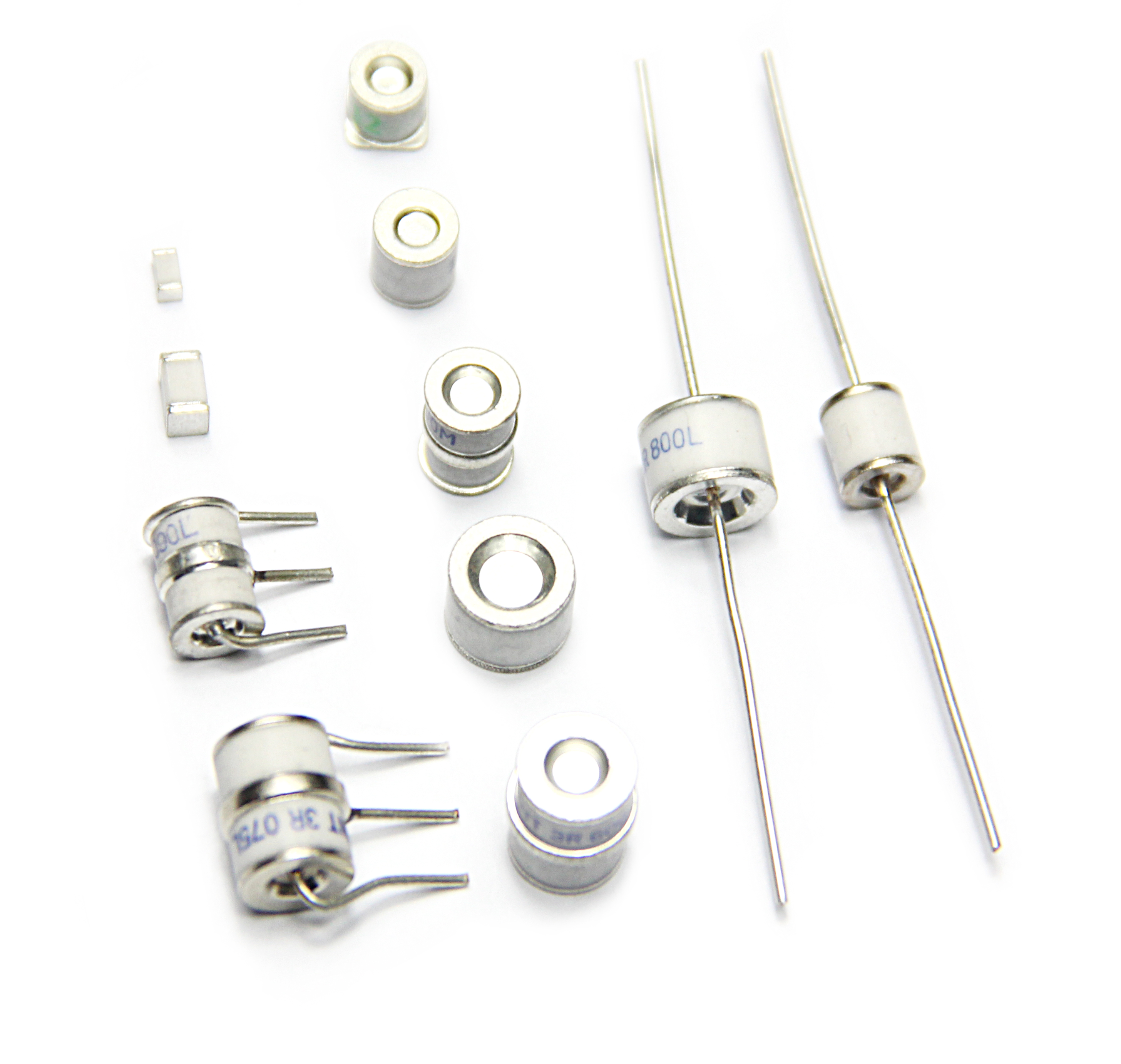

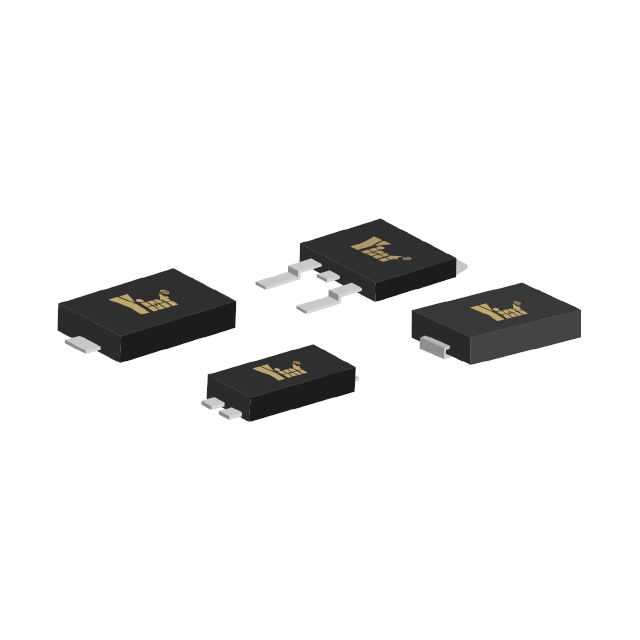

Una linea una cell tutela consilium

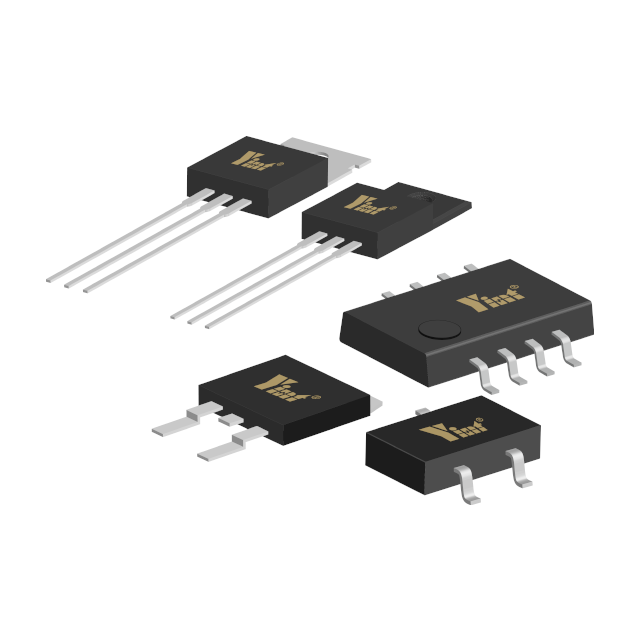

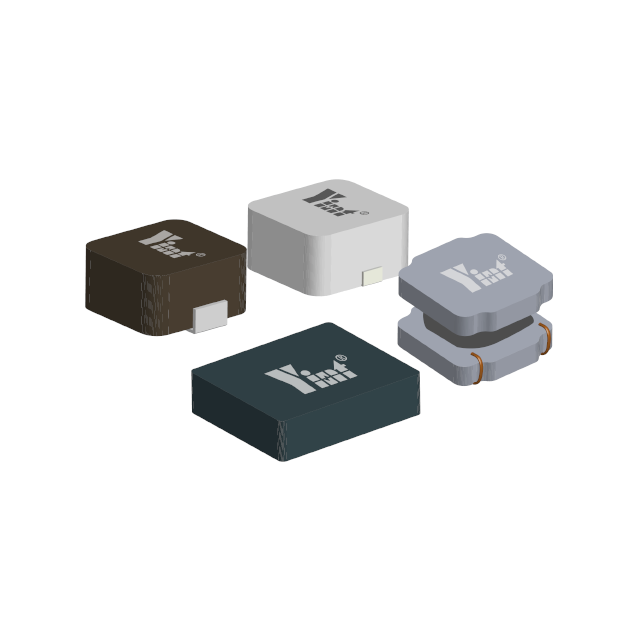

In LVDs mitto finem, singulis data linea additur cum Yint electronic Co. Ltd. Electrostatic praesidio fabrica, quae adoptat sod882 (dfn1006) et sod923 plus-parva sarcina, et ultra-humilis capacitance est <1PF.