The NR5.0SMDJ90CA is a "low clamping" surge/transient protection device developed for 90V bus systems. Its design goal is not simply to pursue higher peak power, but to clamp the bus voltage near the safe window of a 120V withstand voltage DC-DC power chip under critical surge current conditions, thereby significantly reducing the risk of chip breakdown, gate oxide stress, avalanche degradation, and latent failure.

During actual system operation, conditions such as motor feedback, contactor and relay switching, harness parasitic inductance, and load transients continuously introduce transient impacts on the bus side. These processes are typically accompanied by high di/dt and dv/dt characteristics.

It should be noted that transient risk is not entirely determined by the peak amplitude itself. Compared to traditional high-amplitude impacts, the more destructive ones today are often transient processes with faster rising edges and more concentrated energy. Such fast spikes are more likely to act on local weak regions inside the power chip, thereby increasing the risk of device damage.

In 90V DC bus applications, power systems typically select DC-DC chips with a withstand voltage rating of 120V, or adopt solutions with integrated high-voltage MOSFETs and rectification structures. This withstand voltage level provides a certain design margin under steady-state conditions, but its safety window is relatively limited under surge conditions.

When the bus voltage is raised close to or exceeds the chip's withstand voltage threshold during a transient process, the device enters the avalanche or overvoltage operating region. Although this process may not immediately cause functional failure, it triggers continuous thermal stress accumulation and has a long-term impact on device lifetime, thereby reducing overall system reliability.

As semiconductor processes continue to evolve toward smaller line widths, thinner gate oxide layers, and higher integration, the electric field distribution characteristics of devices under transient impact conditions have changed significantly. Local electric field concentration effects become more pronounced, making devices more sensitive to ESD and surge impacts.

In this context, failure modes have also changed. More and more problems no longer manifest as instantaneous breakdown, but appear in forms such as increased leakage current, reduced efficiency, increased output ripple, and intermittent system resets. Such latent failures have hysteresis and concealment, posing greater challenges to long-term stable system operation.

In existing designs, traditional TVS devices typically aim for peak power capability and versatility as primary design goals, making it difficult to precisely control clamping voltage and dynamic resistance simultaneously. Under the same surge current conditions, such devices may not effectively limit the rise of bus voltage.

As a result, the bus voltage may still be raised into the dangerous operating range of the power chip. Although protection devices are configured at the system level, the chip end continues to withstand high voltage stress, and the actual protection effect deviates from the design expectation. This situation of "protection exists but risk is not eliminated" is the key contradiction in current system design.

The design approach is to reverse-engineer key device parameters around the "protection target":

Using a 120V withstand voltage chip as the protection target, within the typical surge current range, clamp the voltage as close to 120V as possible, rather than simply providing a "nominal reverse working voltage" and stopping there.

Reducing dynamic resistance (Rdyn) and snapback rise:

During the surge current rise phase, the clamping voltage is dominated by V ≈ VBR + I·Rdyn. The smaller Rdyn is, the lower the clamping voltage can be maintained even at higher currents.

More attention is given to the clamping and failure boundaries under combined 8/20μs (current) and 1.2/50μs (voltage) surge conditions, emphasizing the "actual voltage seen at the system end."

In high-voltage bus scenarios, low leakage current and batch consistency directly determine long-term stability and customer experience.

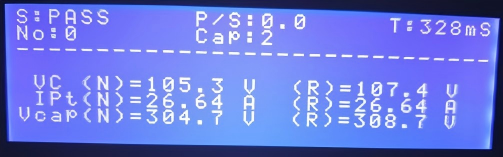

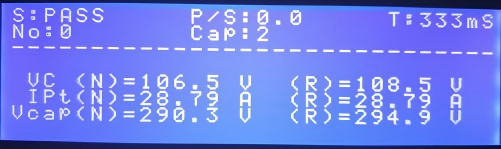

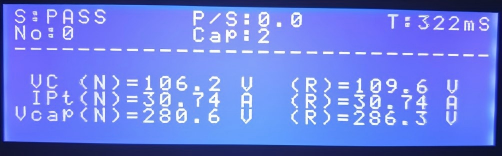

Based on test report data, under 1.4–1.6kV class 1.2/50μs & 8/20μs surge conditions, the device's Vc@Ippmax typically falls within the 114–118V range (varying slightly across different samples and surge points), corresponding to Ippmax of approximately 580–680A. This "clamping window" is specifically designed as an engineering window for 120V withstand voltage chips.

This low-clamping TVS device is suitable for systems powered by a 90V DC bus, particularly in applications requiring high power supply reliability.

In industrial control, servo drives, and robotic systems, it is commonly used for board-level DC-DC power supply front-end protection to mitigate the impact of bus transients on power modules. In energy storage and battery management systems, it can be applied to DC-DC conversion, voltage sampling, and control board power protection under a 90V bus. In automotive, two-wheeled, and light electric vehicle platforms, it can be used for high-voltage accessory power-side protection, with specific applications evaluated based on actual bus voltage levels.

The core advantage of this solution lies in its low-clamping design, which effectively controls the bus voltage under critical surge conditions near the withstand voltage window of 120V power chips, thereby reducing the risk of device breakdown and latent failures caused by transient impacts.

Under high surge current conditions, the device maintains stable clamping capability, reducing the energy absorption burden on downstream circuits and lowering the probability of system reset or abnormal shutdown. Compared to traditional TVS solutions, this device achieves a better balance between dynamic response and actual protection effectiveness.

From an engineering implementation perspective, this device is compatible with traditional TVS in terms of package form and layout, allowing direct integration into DC-DC input stages or bus branch nodes without requiring significant modifications to the existing system architecture.

In practical applications, the device should be placed as close as possible to the power supply input of the protected chip to ensure the shortest protection path and minimal parasitic parameters. PCB design should control trace length and optimize loop area, while also managing input capacitance and trace impedance to suppress transient dv/dt spikes.

For systems with typical surge sources such as long wire harnesses, contactor switching, or motor feedback, a graded protection strategy is recommended. This can be achieved by combining fuses, PTCs, series impedance, and common-mode inductors to progressively limit surge energy, thereby improving overall system robustness.

In terms of verification methods, combined surge testing with 1.2/50μs voltage and 8/20μs current waveforms is recommended, along with load transient and thermal cycling tests to ensure long-term stability of the protection solution under actual operating conditions.

| Sample 1 | Sample 2 | Sample 3 |

|---|---|---|

| VBR1: 103V | VBR1: 101V | VBR1: 104V |

| VBR2: 103V | VBR2: 101V | VBR2: 104V |

| IR1: 0.073μA | IR1: 0.000μA | IR1: 0.000μA |

| IR2: 0.04μA | IR2: 0.009μA | IR2: 0.009μA |

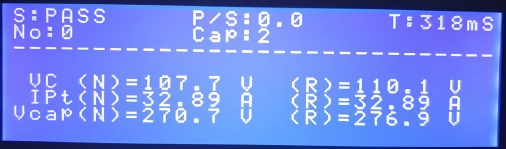

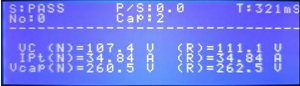

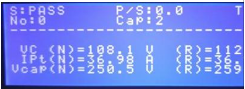

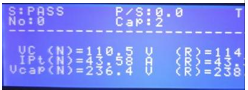

VC1: 105.3V, VC2: 109.6V, VC1: 106.5V, VC2: 108.5V, VC1: 106.2V, VC2: 109.6V, VC1: 107.7V, VC2: 110.1V

IPP1: 26.64A, IPP2: 26.64A, IPP1: 28.79A, IPP2: 28.79A, IPP1: 30.74A, IPP2: 30.74A, IPP1: 32.89A, IPP2: 32.89A

VC1: 107.4V, VC2: 111.1V, VC1: 108.1V, VC2: 112.4V, VC1: 108.6V, VC2: 113.3V, VC1: 109.7V, VC2: 113.5V

IPP1: 34.84A, IPP2: 34.84A, IPP1: 36.98A, IPP2: 36.90A, IPP1: 38.91A, IPP2: 38.93A, IPP1: 41.53A, IPP2: 41.28A

VC1: 110.5V

Designed for the "window protection" requirements of 90V bus or power supplies that may reach corresponding voltage levels, and 120V withstand voltage power supply chips, this solution utilizes a lower surge clamping voltage and a verification method oriented towards actual surge waveforms. It helps customers significantly reduce the overvoltage stress and long-term reliability risks of DC-DC chips without major system architecture changes. For bus protection scenarios pursuing "lower clamping voltage and higher system stability," the NR5.0SMDJ90CA can serve as an upgrade over traditional TVS diodes in the same class.

Hot News

Hot News